新品推荐

芯晶图电子专业芯片代理公司,提供更优质的产品及技术支持

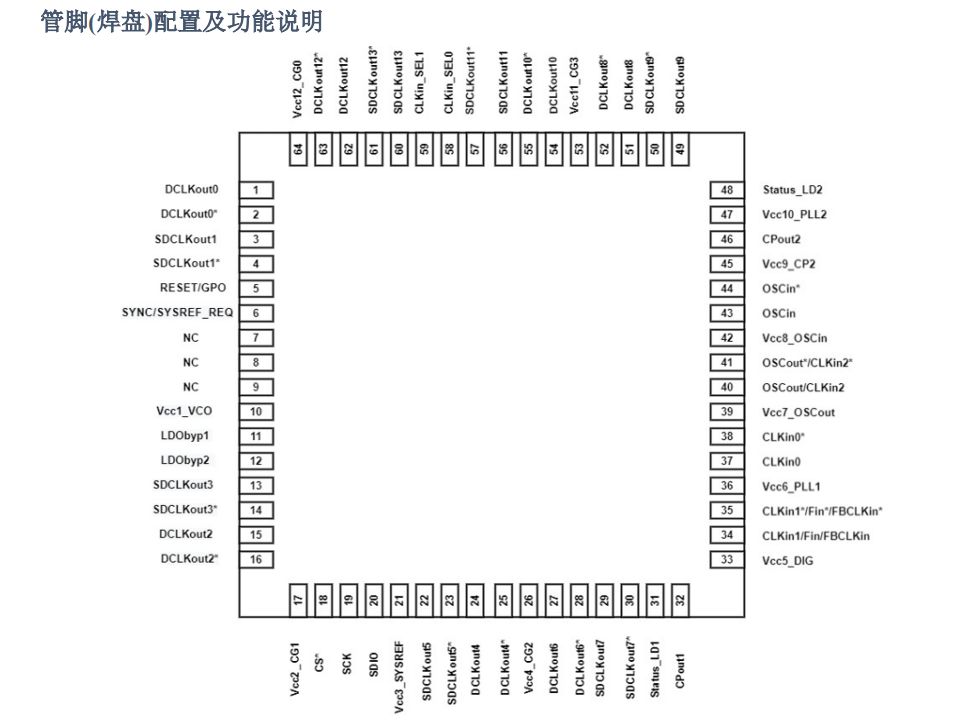

SC6301 是高性能时钟调节器,支持 JEDEC JESD204B。可Pin to Pin兼容LMK04828。当使用设备和 SYSREF 时钟时,PLL2 的 14 个时钟输出可配置去驱动 7 个 JESD204B 转换器或其他逻辑设备。SYSREF 可以使用直流和交流耦合来提供。不仅限于 JESD204B 应用, 14 个 输出均可单独配置为传统高性能时钟系统输出。

Copyright © 2024 深圳市芯晶图电子技术有限公司. All Rights Reserved.